@ExcitedSpider

2018-01-13T11:04:01.000000Z 字数 6422 阅读 2645

计算机组成原理复习(2)

硬布线、微程序的输入输出 输入:IR,状态字REG,时序信号 等

输出:一系列控制信号(微指令)

如何判断水平型/垂直型微指令? 一条指令可表示很多微命令——水平

一条指令只能表示很少的微命令——垂直

流水指令技术

串行传输中的数据传输速率 波特率:每秒钟通过信道传输的总位数,包括起止校验信息等位

比特率:每秒钟通过信道传输的信息量的位传输速率

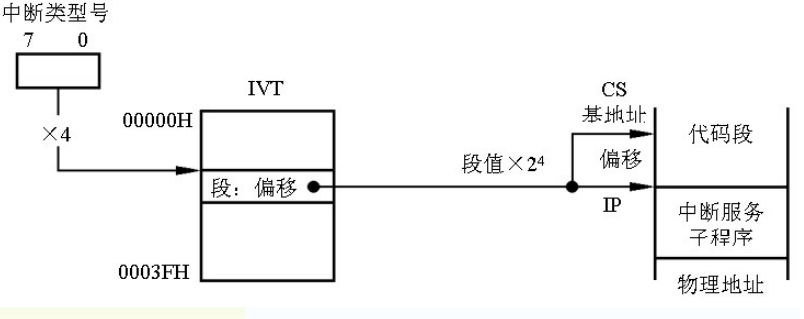

实模式下使用中断向量表

字扩展时外接译码器CS#的逻辑:需要未使用的地址线为0,且MEMR#与MEMW#信号不都为0才有效

例题

某磁盘组有 6 个盘片,最外两侧盘面为保护面、不记录信息。盘片存储区域内径为

对于向量中断,简述中断响应的功能及各个阶段的具体任务。并说明 I/O 中断请求被响应的条件。

某计算机的主频为 50MHz,与某个数据宽度为 32 位、数据传输率为 32Kbps 的设备进行数据 I/O 时,程序查询方式的一次查询操作需 200 个时钟周期,一次数据传送操作需100 个时钟周期,程序中断方式的一次中断处理需 500 个时钟周期。 + = = = =

某 CPU 的主频为 500MHz、CPI等于5,假设某外设数据传输率为0.5MB/s,采用中断方式进行数据传送,以4B长度为传送单位,对应的中断程序共18条指令,中断处理的其它开销相当于 2 条指令时间。 + = = = = = = = = =

某 32 位宽度的同步总线中,总线时钟频率为66MHz,若每个总线传输周期需要4个时钟周期,请计算该总线带宽。若想提高总线带宽,可采取哪些措施?

为什么要进行总线仲裁?链式查询方式仲裁时,各主设备的仲裁逻辑是什么、有什么特点?计数器定时查询方式仲裁时,查询为什么要定时进行?如何实现循环优先级仲裁?

在起止式异步串行通信协议中,若信息格式为 1 个起始位、7 个数据位、1 个停止位,约定波特率为 3600bps,请问每秒最多能传输多少个字符?

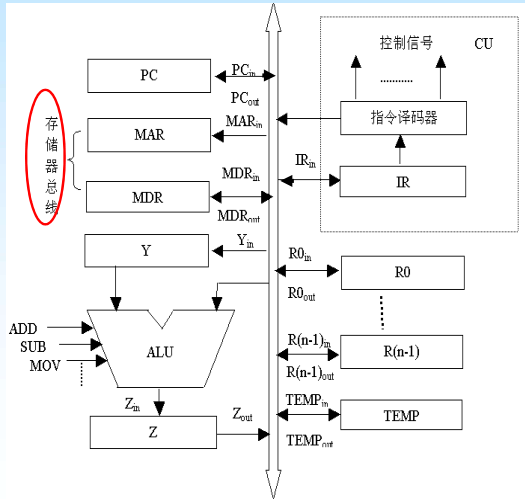

单总线数据通路的 CPU 结构如图所示,PC 具有计数功能。写出下列指令的微操作命令序列。

t1 : PC out 、 MAR in , Read t2 : WMFC t3 : MDR out 、 IR in t4 : R0 out 、 Y in t5 : R1 out 、 ADD 、 Z in t6 : R2 out 、 MAR in , Write t7 : Z out 、 MDR in , WMFC t8 : End

联合控制方式实现同步控制与异步控制间转换的思路是什么?需要哪些微操作控制或状态信号?实现相互转换的原理是什么?

某 CPU 主频为 200MHz,每个机器周期平均包含 4 个节拍周期,每个指令周期平均包含 3 个机器周期(其中有 2 个机器周期需要访存)。 =

某微程序控制器中,CM 容量为 512×40 位,微指令采用水平型格式,顺序控制字段采用下址法+测试网络法(断定法),测试网络有 2 种外部测试条件。 = + =

将指令执行过程分为取指 IF、译码 ID、取数 OF、执行 EX、写结果 WB 共 5 个阶段,各阶段的操作时长分别为 10ns、5ns、10ns、8ns、10ns。若将这 5 个阶段组织成线性流水线,则 (3) 流 水 = = = 流 水 = = 串 行 流 水 = =

某指令系统中,指令字长为 16 位,指令操作码采用扩展编码法,有单地址指令、双地址指令两种指令。若每个地址码均为 6 位,且双地址指令为 A 条,则单地址指令最多有多少条? - -

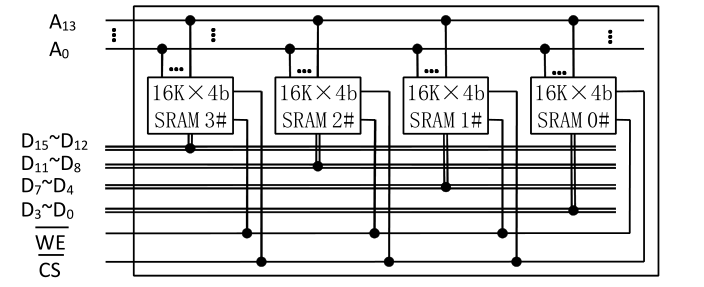

某容量为 16K×16bit 的 SRAM 芯片,其地址引脚(线)、数据引脚(线)各是多少? = =

若用 8K×8bit SRAM 芯片构成 16K×16bit SRAM

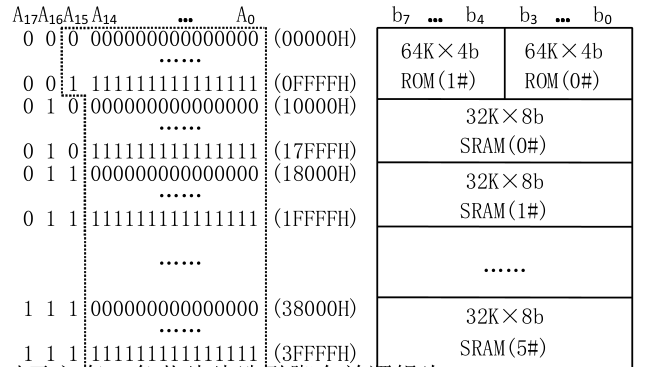

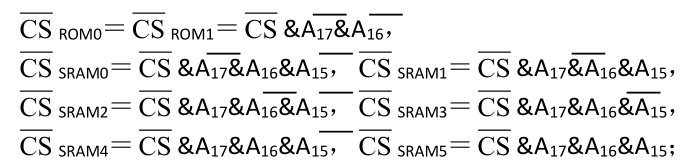

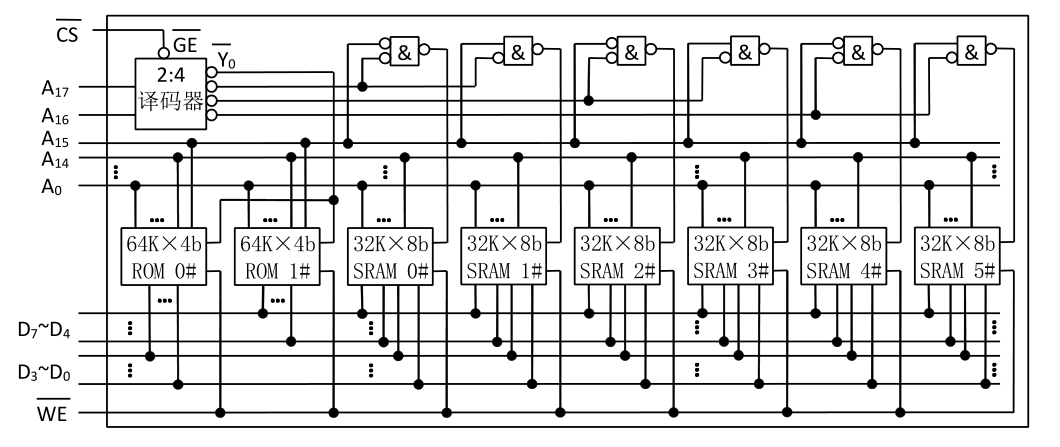

某计算机中,CPU 有 20 根地址引脚(A 19 ~A 0 )、8 根数据引脚(D 7 ~D 0 ),控制引脚由 ADS 、IO/ M 及 R/ W 三根引脚组成,若主存配置为 64KB 的 ROM 及 192KB 的 SRAM ,ROM 在主存空间的低端。现有 64K×4 位 ROM 芯片、32K×8 位 SRAM 芯片若干。 =

某计算机中,约定主存按字节编址,CPU 有 20 根地址引脚、8 根数据引脚,配置有 64KB 的 Cache,若 Cache 与主存采用 4 路组相联映像、块大小为 16B。

为什么虚拟存储器中存在虚存-辅存地址变换?为什么虚拟存储器的管理表格通常

冯·诺依曼模型的存储程序原理包含哪些内容、对计算机硬件和软件有哪些要求?冯·诺依曼模型计算机的特点有哪些?