@Velaciela

2019-07-08T10:07:56.000000Z

字数 421

阅读 69

研究生硬件项目材料

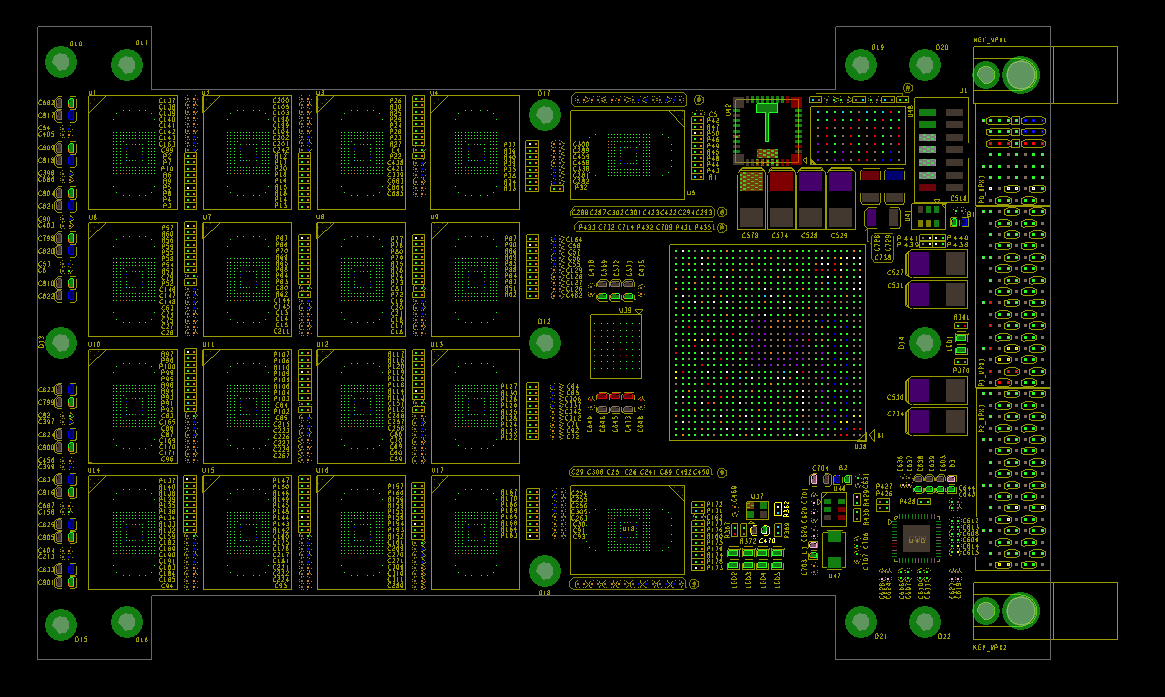

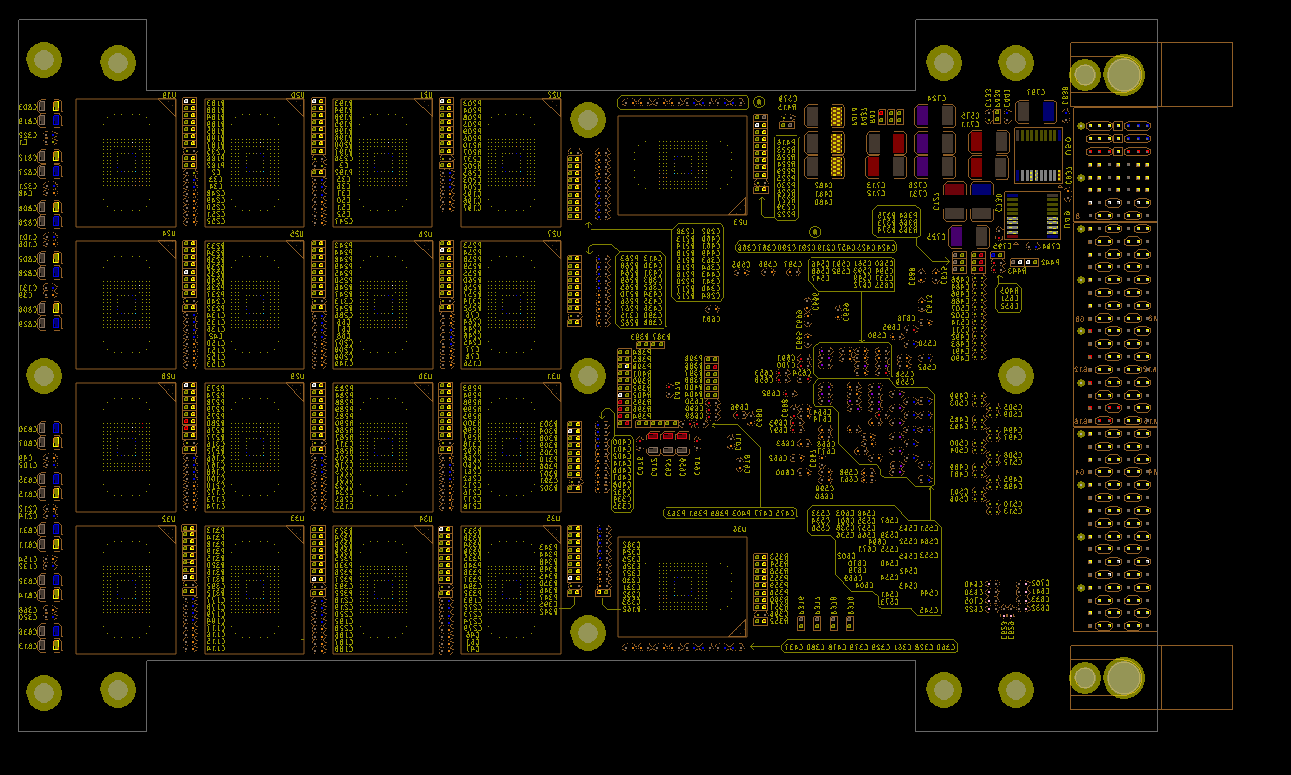

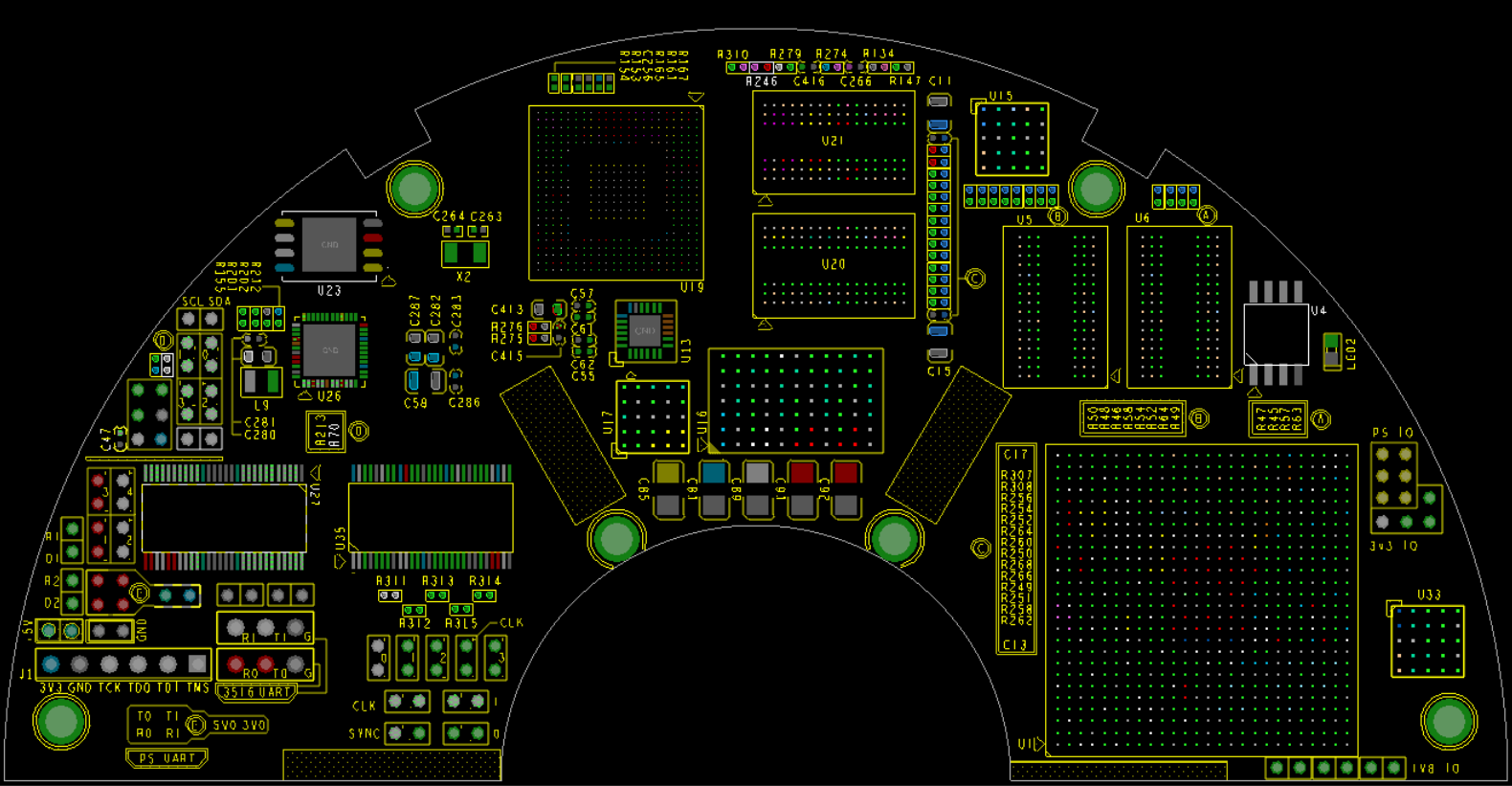

1、Xilinx K7 + 36片eMMC 布局布线 | 2015年

有早期版本,这版修改了一些地方。

为了美观的布局布线,基本重新做了一遍。

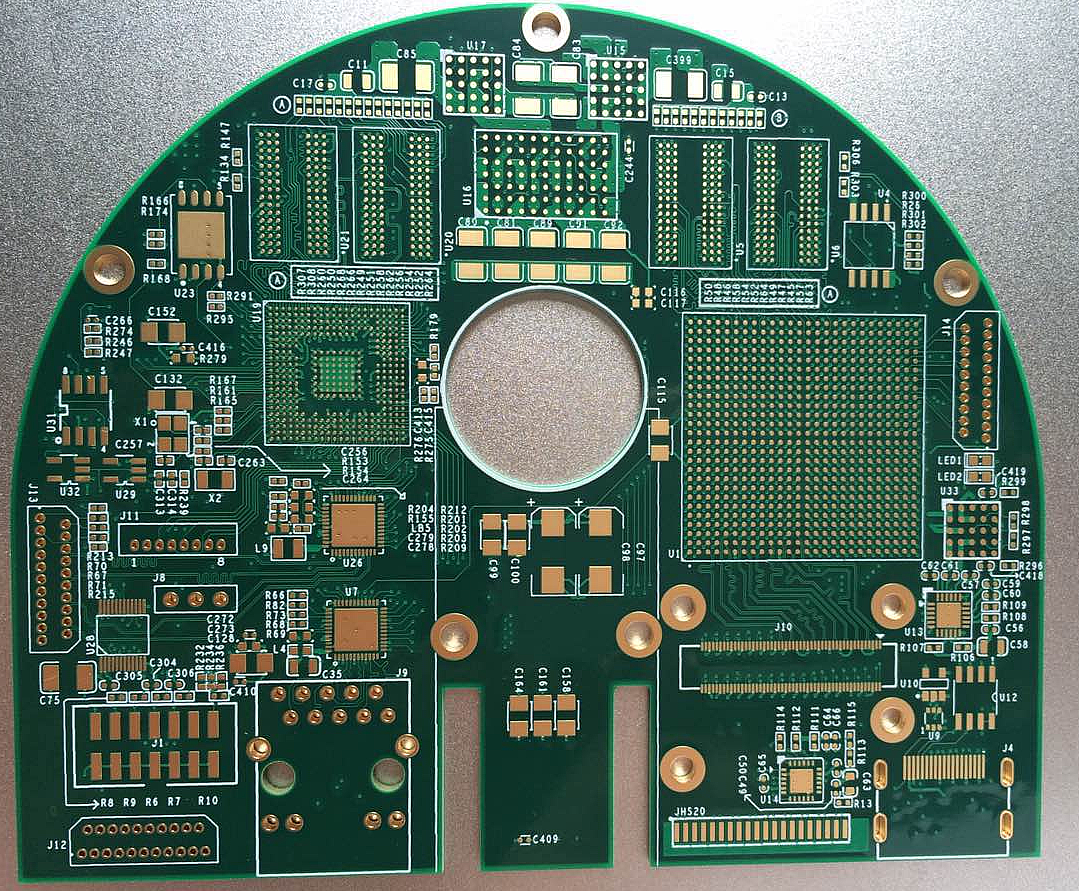

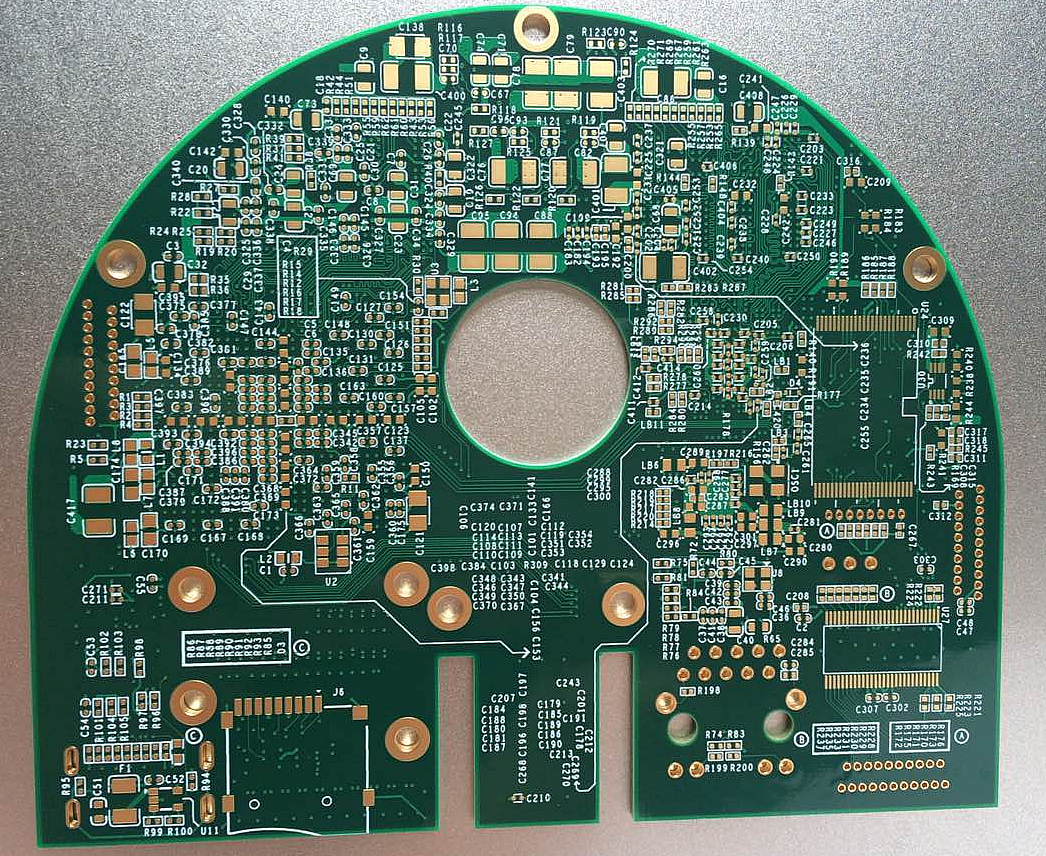

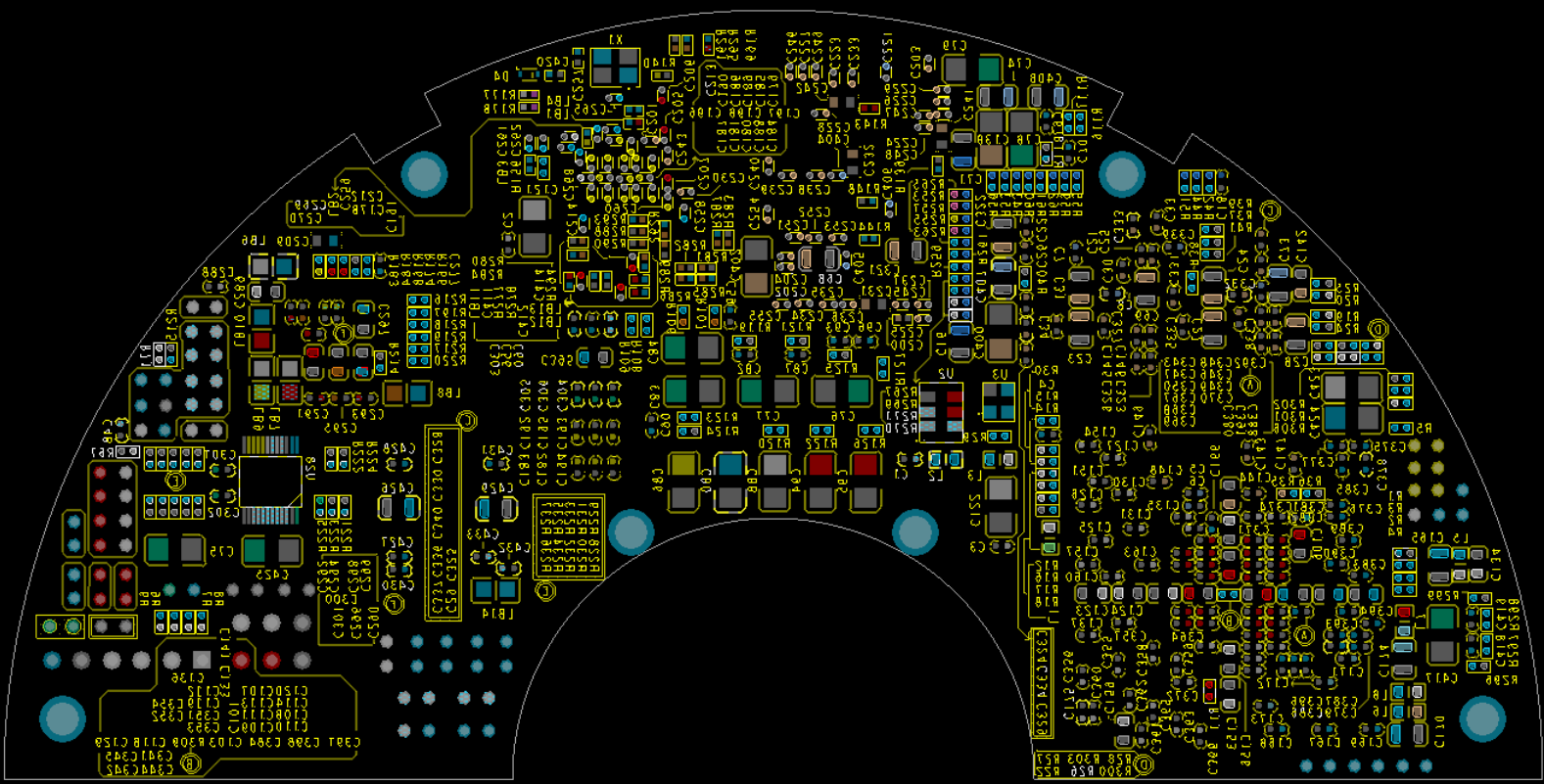

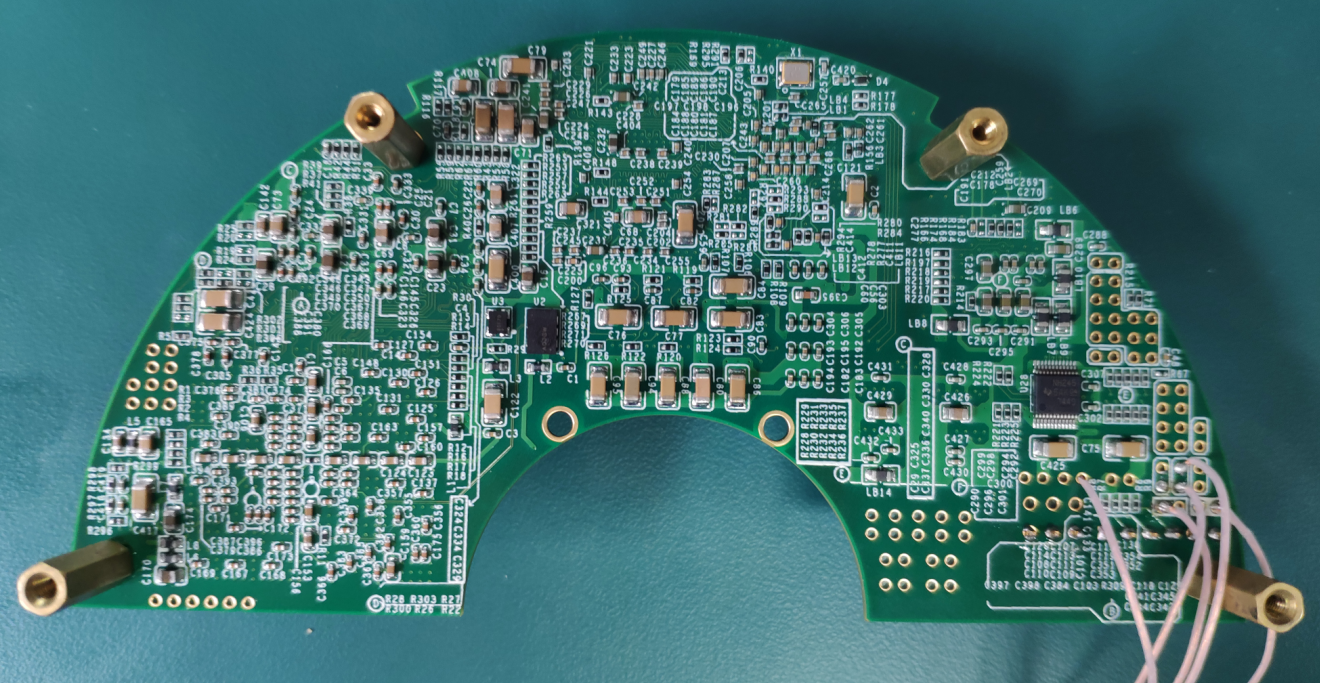

2、Xilinx Z7 + Hi3516 + 两组DDR2 布局布线 | 2017年

(由于时间比较紧,不重要的部分较为凌乱)

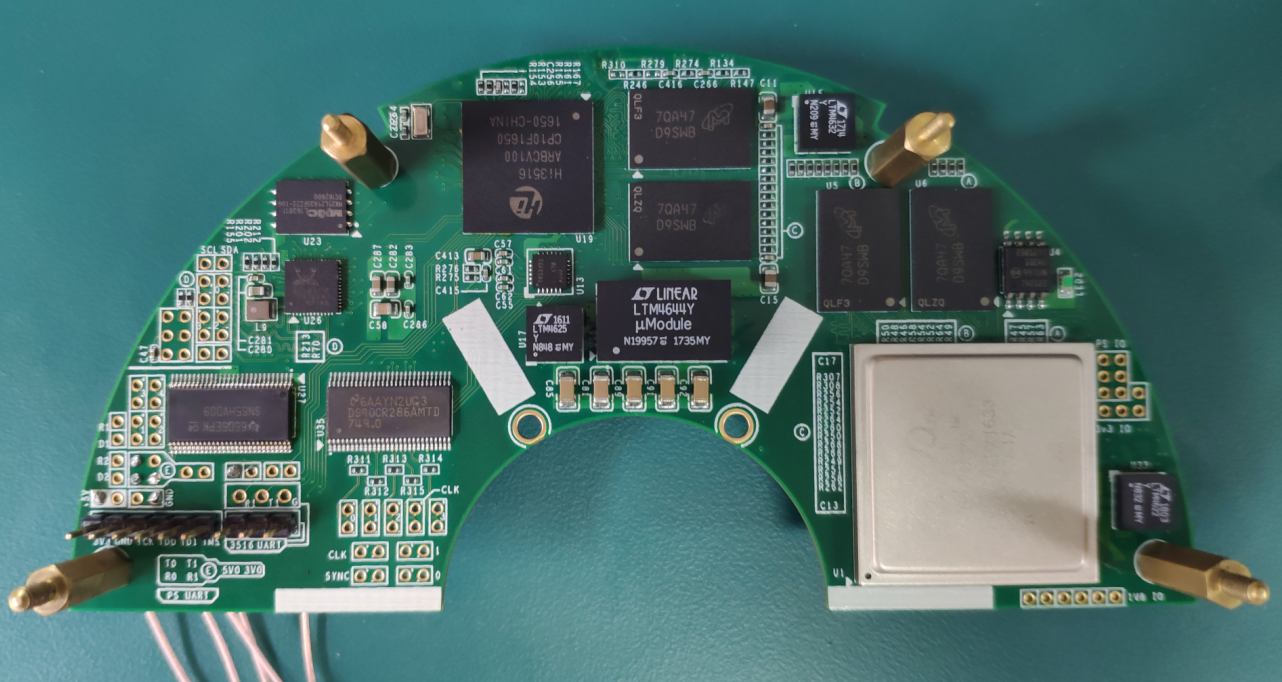

【2018 年前 第二版】//20190708无聊更新

……画的最后一块板子……

2018年春节后 3月开始商汤实习

3、硬件调试

Xilinx K7 + 4片DDR3 : 调试Xilinx的DDR IP核,把单一接口封装成多通道供多个模块进行数据交换。

调试ZYNQ,ARM与FPGA逻辑部分通过AXI总线传输DDR3数据(已有例程修改)。

调试ZYNQ,DDR3通过AXI总线与经过RAM/FIFO缓冲的2.4GSPS AD/DA做数据传输(实验室之前已有积累)。