@aod321

2018-12-17T08:33:28.000000Z

字数 993

阅读 555

HEDS9040驱动笔记

光电编码器

前言

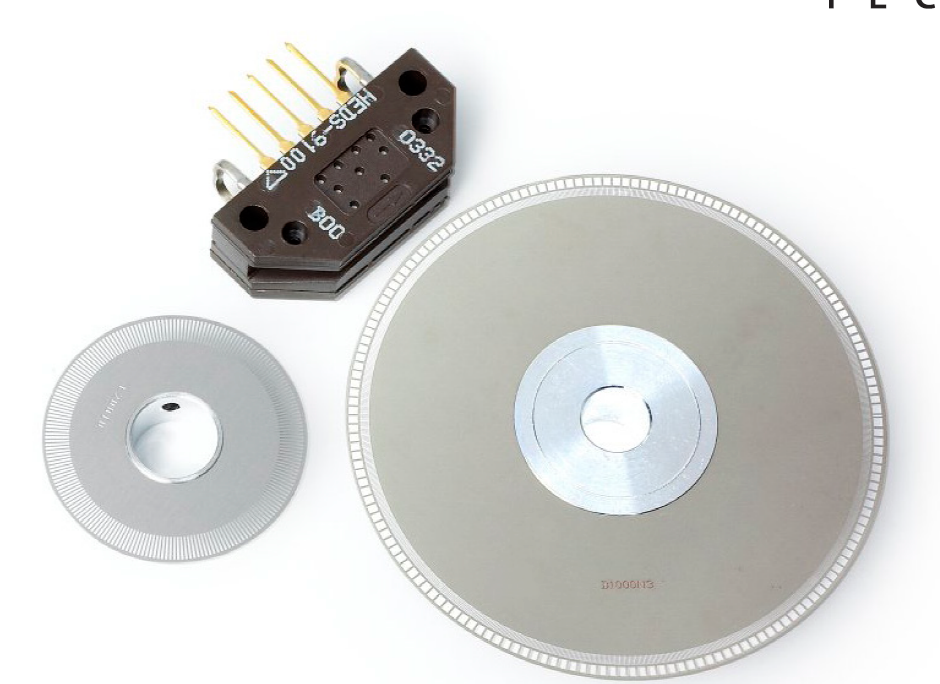

最近拿到一个新的光电编码器,要用FPGA驱动它。二话不说就拿起手册看,看完发现原来这玩意儿就是一个脉冲计数,都谈不上什么"驱动",因为在笔者字典中"驱动"是个很高大上的词,一般要涉及到一系列复杂的协议、时序或者寄存器配置等等。

基本逻辑

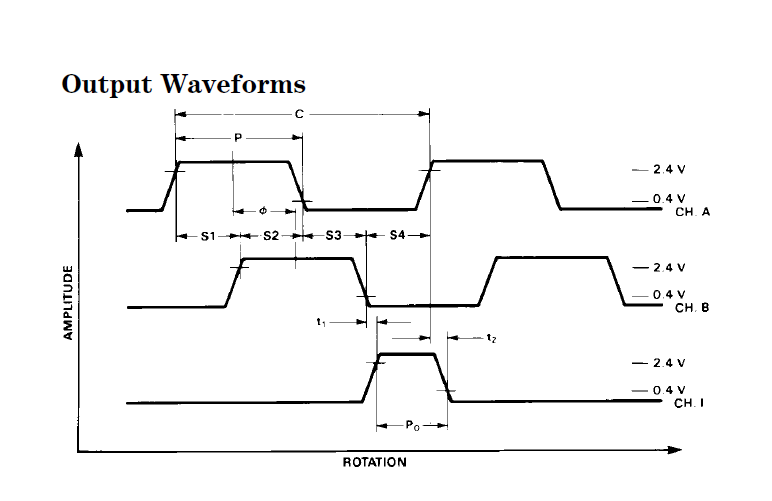

光电编码器系统由码盘和接收头两部分组成,接收头内部含有红外发送和接收对管,当红外光遇到码盘上的间隔被吸收时,下方的接收头接收不到红外光于是会返回一个脉冲。HEDS9040内部含有两对红外对管,当红外光被吸收时,会从CHA和CHB两个通道输出相位相差一半的脉冲波形,见下图所示。

所以基本逻辑如下:如图所示,红色线:以A信号为准,当A信号为上升沿的时候,B通道为高电平,则系统为CW方向(顺时针),相反地,看绿色线:如果此时B通道是低电平的话则方向为CCW(逆时针)。

三通道的输出波形如上图,多了一个I通道,I通道只在检测到零位时又一次高电平,时间从B的下降沿延续到A的上升沿。

Verilog 代码

有了上面逻辑以后,代码写起来很容易,就是基本的组合逻辑。

// **********//本Verilog 代码仅为说明逻辑,实际可综合代码请修改检测上升沿方式//**********always @(posedge clk) begincha_buf <= cha;chb_buf <= chb;chi_buf <= chi;end//第三通道得到信号,清零always @(posedge chi_buf or posedge reset) beginif(reset) count<=0;else beginif(chb_buf) begincount<0;endendendalways @(posedge cha_buf or posedge reset) beginif(reset) count<=0;else beginif(!chb_buf) begincount<=count-1;endelse begincount<=count+1;endendend

角度换算公式

2048细分

根据角度换算公式,我们就可以把count数据乘360再左移10位就可以得到角度信息或者直接发给下一级设备处理了。