@floatsd

2016-06-09T18:24:24.000000Z

字数 2505

阅读 1092

实验六 A/D转换实验

note_DSP

1 实验目的

1、了解DSP实验系统中A/D转换电路的工作原理;

2、熟悉A/D转换模块的配置方式;

3、掌握A/D转换模块的编程和数据处理方法。

2 实验原理

2.1 A/D模块的特点

- TMS320F2812片内有1个带采样保持电路的12位的A/D 转换模块。主要特点如下:

- 带两个采样保持器的12位ADC;

- 模拟量输入范围0.0V~3.0V;

- 转换时间在25MHZ的ADC时钟下为80ns;

- 16通道模拟电压输入;

- 自动排序功能可以一次触发16路A/D,每次转换的通道可用软件编程选择;

- 排序器可以工作在2个独立的8通道排序或者16通道级联排序模式;

- 转换结果存储在与每个通道对应的结果寄存器中,转换结果=4096×Vin/3;

- 有多重触发A/D转换方式:软件启动,EVA和EVB;

- 中断控制方式灵活,可以在每次转换结束或每隔一次转换结束触发中断。

2.2 ADC模块的引脚信号

- ADC模块的引脚由模拟量输入部分、ADC设置部分和ADC电源三部分组成。

- 模拟量输入部分:

- A通道输入:ADCINA0~ADCINA7

- B通道输入:ADCINB0~ADCINB7

- ADC基准部分:

- ADC电压基准输出(2V):ADCREFP

- ADC电压基准输出(1V):ADCREFM

- ADC外部电流偏置电阻:ADCRESEXT

- 供TI测试用引脚(需悬空):ADCBGREFIN

- ADC模拟地: AVSSREFBG

- ADC模拟电源(3.3V):AVDDREFBG

- ADC公共地(接模拟地):ADCLO

- ADC电源:

- ADC模拟电源(3.3V):VDDA1、VDDA2

- ADC模拟地:VSSA1、VSSA2

- ADC数字电源(1.8V):VDD1

- ADC数字地:VSS1

- ADC的I/O 电源(3.3V):VDDAIO

- ADC的I/O 地:VSSAIO

- 模拟量输入部分:

2.3 ADC转换模块的编程和程序流程

- 初始化DSP系统;

- 设置PIE中断矢量表;

- 初始化ADC模块;

- 将ADC中断的入口地址装入PIE中断向量表,开中断;

- 软件启动ADC转换;

- 等待ADC中断;

在ADC中断中读取ADC转换结果,软件启动下一次ADC中断。

- 作例程如下:

AdcRegs.ADCTRL1.bit.SUSMOD=0; //模式0,仿真挂起被忽略。AdcRegs.ADCTRL1.bit.ACQ_PS=0; //设置脉冲宽度AdcRegs.ADCTRL1.bit.CPS=0; //内核时钟频率. Fclk = CLK/1.AdcRegs.ADCTRL1.bit.CONT_RUN=0; //开始-停止模式,产生EOS 信号后,排序器停止,除非排序器复位,否则排序器从停止后的状态开始。AdcRegs.ADCTRL1.bit.SEQ_CASC=0; //双排序器模式,SEQ1 和SEQ2 作为两个独立的排序器工作。AdcRegs.ADCTRL3.bit.ADCBGRFDN=3; //带隙和参考电路上电AdcRegs.ADCTRL3.bit.ADCPWDN=1; //除带隙和参考电路外其他模拟电路上电AdcRegs.ADCTRL3.bit.ADCCLKPS=10; //内核时钟分频器,ADCCLK=75/20AdcRegs.ADCTRL3.bit.SMODE_SEL=0; //选择顺序采样模式.AdcRegs.MAX_CONV.bit.MAX_CONV=1; //选择转换通道ADCINA6 & ADCINA7AdcRegs.CHSELSEQ1.bit.CONV00=6; //ADCINA6—等于对功放板电源电压24V衰减至约十分之一,即2.4V.AdcRegs.CHSELSEQ1.bit.CONV01=7; //ADCINA7—参考输入,电压幅值可调.AdcRegs.ADC_ST_FLAG.bit.INT_SEQ1_CLR=1; //清除中断标志位AdcRegs.ADCTRL2.bit.RST_SEQ1=0; //复位排序器到0 状态AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1=1; //使能SEQ1 中断 (every EOS)AdcRegs.ADCTRL2.bit.INT_MOD_SEQ1=0; //每个序列转换结束,INT SEQ1置位AdcRegs.ADCTRL2.bit.EVA_SOC_SEQ1=0; //禁止 EVA SOC 启动SEQ1AdcRegs.ADCTRL2.bit.EXT_SOC_SEQ1=0; //外部信号无操作

3实验内容

3.1 实验准备及观察结果

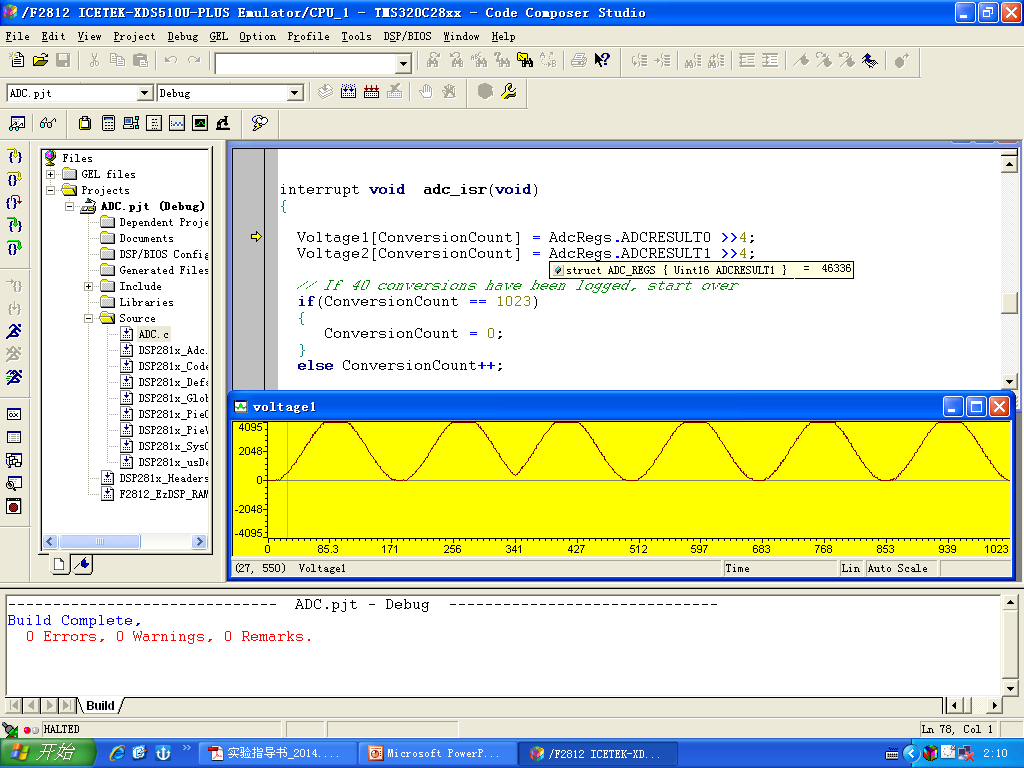

- 连接实验设备,将波形发生源连入A/D输入端,在Emulator方式下打开ADC.pjt,编译,下载程序,打开观察窗口,运行观察到如下结果:

- 停止运行,调整信号发生源的赋值和频率后再次运行,可以看到观察窗口内波形发生变化。

4 思考题

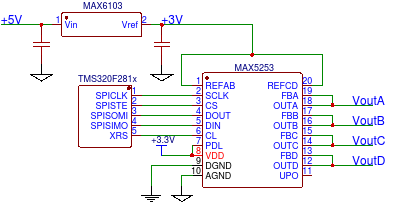

思考题1:如果F2812 的片内ADC 无法满足要求,如何扩展ADC 芯片。提示:可以通过SPI接口或外部扩展接口(XINTF)扩展串行或并口接口的ADC芯片。

- 通过SPI接口扩展D/A转换器MAX5253,设计接口电路如下:

- 并有软件配置如下步骤:

- 配置SPI模块

- 清零SPI SW RESET位(SPICCR.7),软件复位SPI;

- 设置SPI寄存器,如数据格式、波特率、工作与时钟模式、引脚功能;

- 置位SPI SW RESET位,使SPI退出复位状态,进入工作状态;

- 写数据到SPIDAT或SPITXBUF,(主模式下就启动通信过程);

- 数据传输结束后(SPISTS.6=1),读取SPIRXBUF中的数据。

- 配置SPI模块

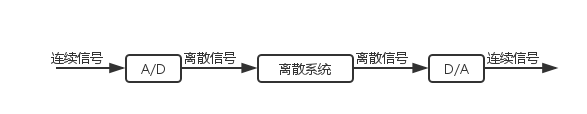

思考题2:试针对某一数字信号处理或数字控制系统,简述A/D 转换器的功能?

- 最基本的数字控制系统流程大致如下:

- 可以看到A/D模块的作用是将模拟信号转换成数字信号,在开环控制中,由于可控器件的发展,直接由PWM数字输出控制量,省略A/D和D/A模块并不是不可能,但特别是涉及到反馈的闭环控制,一定会有观测输出,这个时候一定要有A/D模块负责把需要观测的模拟信号采集为数字信号,才能送入计算机数字控制系统中进行运算。